International Research Journal of Human Resources and Social Sciences Vol. 4, Issue 1, January 2017 Impact Factor- 5.414

ISSN(O): (2349-4085) ISSN(P): (2394-4218)

© Associated Asia Research Foundation (AARF) Website: www.aarf.asia Email: editor@aarf.asia, editoraarf@gmail.com

# STUDY OF CRITICAL FAULTS AND ALGORITHMS OF REPAIR IN PROPOSED TRIANGLE MIN

## **Amardeep Gupta**

Head PG Dep't of Computer Sc and IT D A V College, Amritsar, Punjab

#### **ABSTRACT**

This paper analyses Fault Tolerance of the proposed MIN Triangle. Routing tag provides the algorithm to pass the data from source to destination in a network. The path lengths available from source to destination in Triangle MIN have been found.

**Keywords:** Architecture, Fault Tolerance and repair, Path Lenghts, routing tag redundancy graph, algorithms of routing.

### ARCHITECTURE OF TRIANGLE NETWORK

The network is an Irregular MIN of size N\*N. It has N sources and N destinations. The Triangle network of size  $2^n*2^n$  consists of (2m-2) stages. This network has ( $2^n$  -2) no. of switches of size 3\*3 and  $2^{n-1}$  no. of switches of size 2\*2.Each source is connected to one SE in each group with the help of N multiplexers[1] and is connected to the output with equal number of demultiplexers.

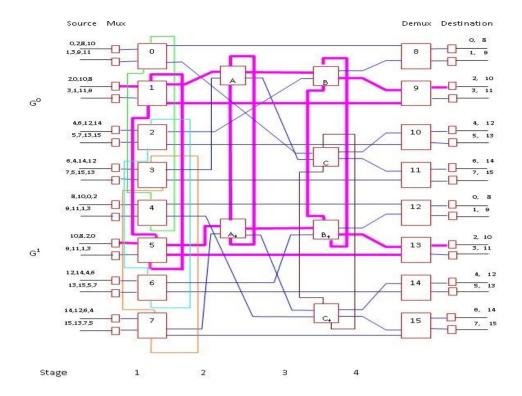

The network comprises of two identical groups[7] of SEs, named as G<sup>0</sup> and G<sup>1</sup>. The network of size 16\*16, with labeled switches is shown in Fig1.

Fig 1: All paths available from source 0000 to 1010 destination in Triangle MIN

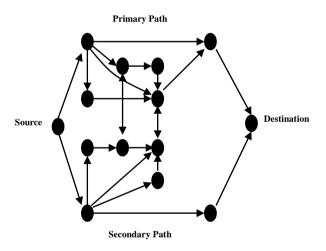

Fig 2: Redundancy graph of Triangle MIN

# **REDUNDANCY GRAPH**

# Routing Algorithm and analysis of proposed Triangle MIN in the presence of faults

Let the source and destination in binary be represented as

$$S=S_{n-1}....S_1S_0$$

$$D=D_{n-1}.....D_1D_0$$

Let the routing tag[6][8] Koppelman D. M et al. (1990) be denoted as  $t_m t_{n-1} \ t_{n-2} \dots t_0 t_{dm}$ , where

t<sub>m</sub> is the multiplexer control bit.

$t_{n-1}$  is the bit being sensed by SEs of the first stage.

t<sub>n-2</sub> is the bit being sensed by SEs of the second stage.

. . . . . . . . . . . . .

$t_0$  is the bit being sensed by SEs of the last stage.

t<sub>dm</sub> is the demultiplexer control bit.

The function for routing tag and routing procedure is

$t_i = d_i$  for all  $(0 \le i \le n-1)$  where  $n = \log_2 N$

$$t_i = [(S_{n-1} \quad d_{n-1}) + (S_{n-2} \quad d_{n-2}) + \dots + (S_{n-i} \quad (-) I_{n-i})]$$

for all  $n \le i \le n$ , where  $\oplus$  is 'exclusive or'

$t_m = s_{n-1}$

$t_{dm}=d_{n\text{-}1}$

Routing example from source 0000 to all destinations for the Triangle Network has been listed in Table 1.

Table 1: All Path Lengths available in Triangle Network

| Source      | Destination | Path Lengths<br>Available |

|-------------|-------------|---------------------------|

|             | 0000        | 2,4                       |

|             | 0001        | 2,4                       |

|             | 0010        | 2,4                       |

| 50 <u>-</u> | 0011        | 2,4                       |

| -           | 0100        | 4                         |

| 93          | 0101        | 4                         |

| 32          | 0110        | 4                         |

| 0000 -      | 0111        | 4                         |

|             | 1000        | 2,4                       |

|             | 1001        | 2,4                       |

|             | 1010        |                           |

|             | 1011        | 2,4<br>2,4                |

|             | 1100        | 4                         |

|             | 1101        | 4                         |

|             | 1110        | 4                         |

|             | 1111        | 4                         |

The function of the path lengths available in Triangle MIN is  $log_2(N)-2$ ,  $log_2(N)$ .

The path length for favorite memory module is  $\log_2(N)$ -2.

## FAULT-TOLERANCE AND REPAIR

The proposed MIN satisfies the Fault-Tolerant criteria[3][5] because it can work in the presence of certain faults. If there is fault in the primary path then secondary path will be chosen for routing the data. Moreover, there are multiple paths from one type of source to one type of destination which makes this network more Fault-Tolerant and reliable Kamiura N et al. (2000)

The auxiliary links in all the stages except the last one provides the alternate route[4] of the data. The critical case is when the fault is present in the SE in same loop. In this case certain pair of source and destination shall be disconnected.

Theorem: Different path lengths are available for routing from source to destination in primary and secondary routes.

**Proof:** The probability of request forwarding within stages of the Triangle Network is different. Moreover, the auxiliary links are available in all the SEs in all the stages except the last one. If fault in any of these SE happens, then the data will be routed to the auxiliary SE[6] in the same stage through auxiliary links.

Lemma: Triangle Network maintains the connectivity in the presence of the fault, only if the auxiliary SE in the same stage is Fault-free.

Repair: To rectify, just replace the loop engaged in the faulty components with the new one.

Fig 1 shows the multiple paths available from source 0000 to destination 1010.

The routing tags used to transfer the data from source 0000 to destination 1010 in the respective faults of stage 3, where the secondary path is established by complimenting the MSB of the routing tag.

#### **CONCLUSION**

It is clear that the proposed MIN is fault tolerant in the presence of faults. For 100% requests generation, Triangle Network passes 50% more requests as compared to comparative Networks. When the critical faults are present in the stage 3 the proposed Triangle MIN, passes 37% of the requests generated.

#### REFERENCES

- 1. J. Arlat, K. Kanoun, and J.C. Lapric, "Dependability Modelling and Evaluation of Software Fault Tolerant Systems", IEEE Transactions on Computers, 39/4, pp. 504-512.

- 2. C. Chen, D.P. Agrawal, and J.R. Burke, dBCube: "a new class of hierarchical multiprocessor interconnection networks with area efficient layout", IEEE Transactions on Parallel and Distributed Systems, 4/12, pp. 1332-1344.

- 3. Bansal P. K., Joshi R. C. and Singh Kuldeep, May 1992, "Quad Tree: a Cost-Effective Fault-Tolerant Multistage Interconnection Network", International Conference IEEE INFOCOM 92, ITALY.

- 4. Jeng M. and Siegel H. J., May 1986, "A Fault-Tolerant Multistage Interconnection Network for Multiprocessor Systems using Dynamic Redundancy", Proceedings 6<sup>th</sup> International Conference on Distributed Computing Systems, pp. 70-77.

- 5. K. Arun. Somani, Vaidya Nitin H., April 1997, "Understanding Fault-Tolerance and Reliability", IEEE Computer Theme (30).

- 6. Padmanabhan K. and Lawis D. H., August 1983, "Fault-Tolerant Schemes in Shuffle/Exchange type Interconnection Networks", Proceedings of International Conference Parallel Processing, pp. 71-75.

- 7. Reddy S. M. and Kumar V. P., August 1984, "Fault-Tolerant Multistage Interconnection Networks", Proceedings 5<sup>th</sup> International Conference on Parallel Processing, pp. 155-164.

- 8. Varma, Interconnection networks for multiprocessors and multicomputers: theory and practice EH 3806.